Xilinx LVDS使用(以DAC AD9736展开)

Xilinx的vivado设计套件中,对于lvds的使用可以选择两种方式,一是使用原语,例如IDDR ODDR这类进行双边沿数据传输的原语,也有IBUFDS等差分转单端的原语,这些原语为LVDS的不同方式提供解决方案。

而我更多的是去使用selectIO这个IP核来实现lvds的传输。

一、LVDS介绍

LVDS(Low-Voltage Differential Signaling)低电压差分信号,这种传输技术可以达到155Mbps以上。

在FPGA上一般可以配置专门的bank作为lvds的用途。而其由于电压幅度(Ex: LVDS 2.5V)低于一般的(CMOS 3.3V),因此可以达到更高得到传输速度。

对于Xilinx FPGA的LVDS25接口,其最高速度可达600Mbsps。

二、AD9736

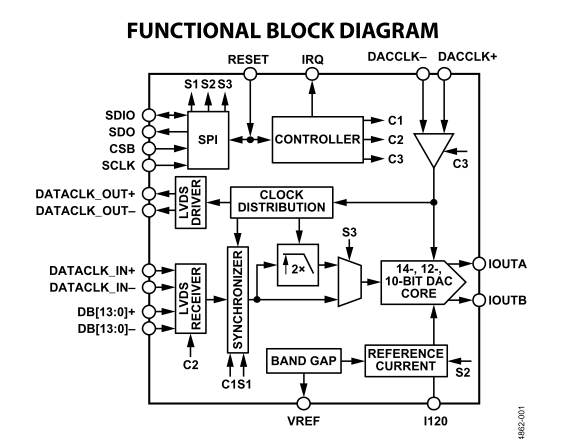

AD9736是ADI的一块14bit 1200MSPS的DAC。其功能框图如下

从功能框图中可以看到,AD9736为了匹配高速做好同步,芯片会给出一个时钟DATACLK_OUT,此外它还具有SPI控制的内部寄存器等。

在设计上,DATACLK_OUT给FPGA,FPGA给出数据与DATACLK_IN,而DAC_CLK则由pll锁相环芯片来产生,一般的FPGA的时钟输出没有pll锁相环来的干净,稳定。

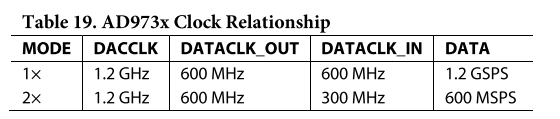

通过阅读数据手册,可以知道通过寄存器的配置,可以配置AD9736为2x模式或者1x模式。具体如下图所示

在2x模式下,其内部会有一个插值滤波器,在两个数据间进行插值,从而使数据时钟可以只要300MHz即可。

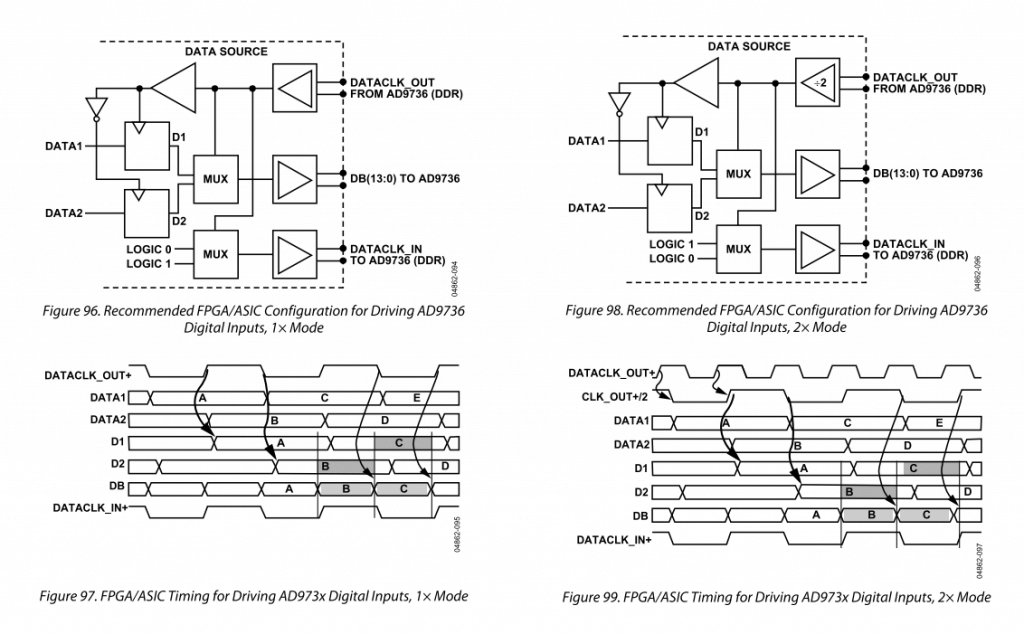

此外数据手册也给出了编程的方案,如下图所示

根据上图,可以看出,其为DDR的传输模式,且为OPPOSITE_EDGE模式。

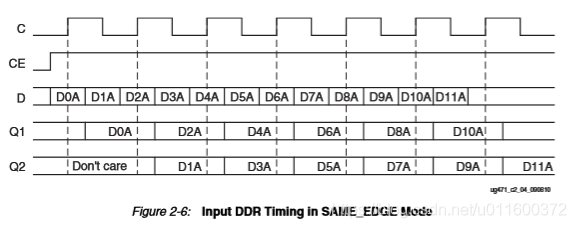

此外还有一种SAME_EDGE模式,如下图所示,

由于DDR的一个时钟会给出两个数据,可以从他给出的是时序图看出,他有两个数据D1 D2组合然后发送给DB输出,这会在后续SelectIO配置中看出来。

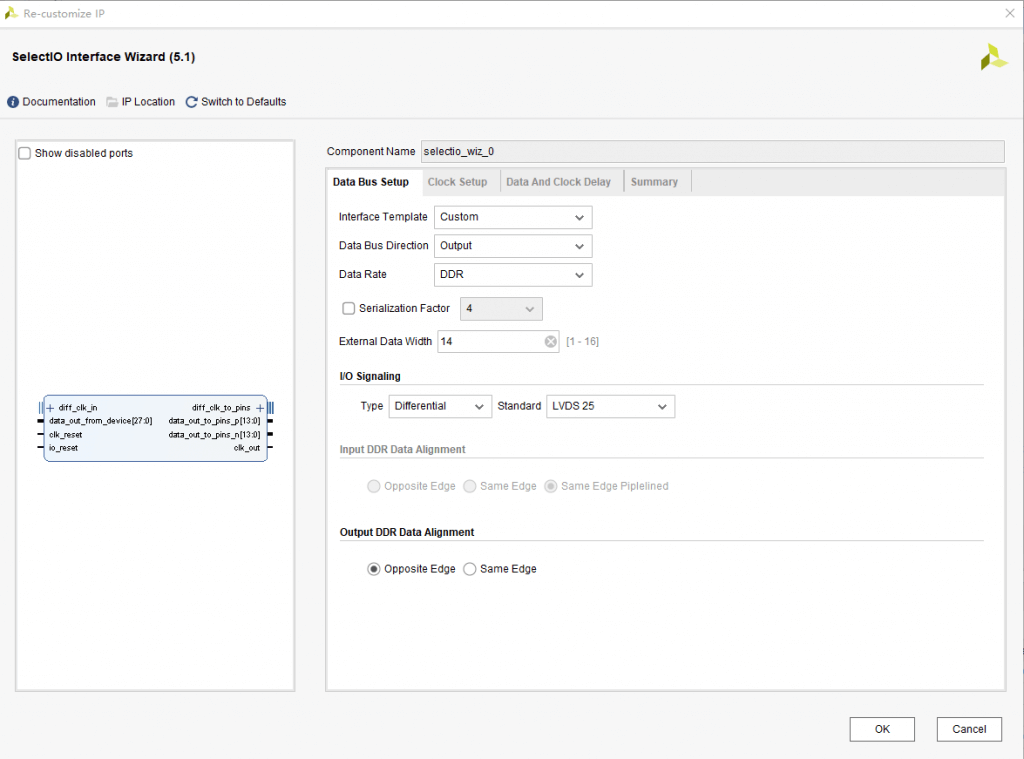

三、SelectIO配置

如上图所示,Interface Template采用Custom;

Data Bus Direction由于是DAC所以是output输出模式;

Data Rate采用DDR模式,此外SDR即为Single Data Rate,比较好的区分,就是看他传输时一个时钟会发送几个数据。DDR一个时钟会给出两个数据,而SDR只给一个。

External Data Width根据DAC是几位的配置成几位,此外selectIO可以通过Serialization Factor进行并转串,进一步提高数据吞吐量。

IO Signaling 则是差分以及LVDS 25

最后的Output DDR Data Alignment则为Opposite Edge。这个的选择前面已经讲过。

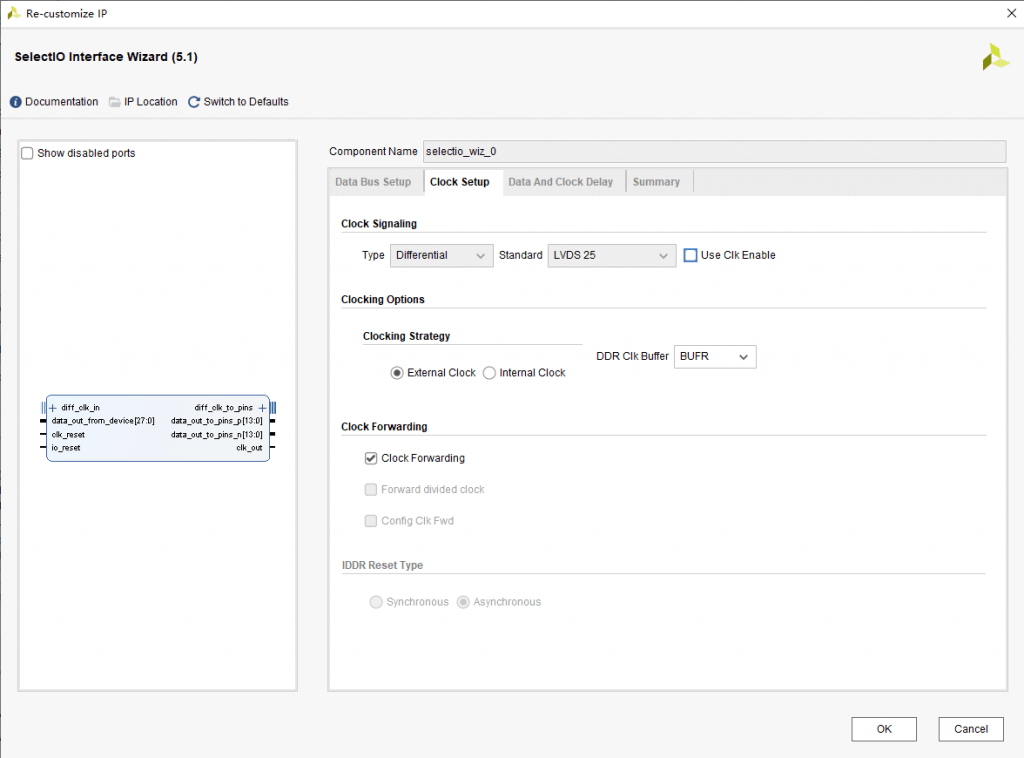

第二页如上图配置,其中Clock Signaling同样是差分 LVDS25电平标准

Clocking Options采用的是外部时钟,因为AD9736有一个DATACLK_OUT,我们将这个时钟输出作为该IP核的时钟,而右边DDR Clk Buffer则是选择相应的原语,将该时钟转化为时钟域的时钟

Clock Forwarding中选择Clock Forwarding,此时该IP核会输出一个差分时钟,这个差分始终与数据同步,供给AD9736的DATA_CLK_IN。

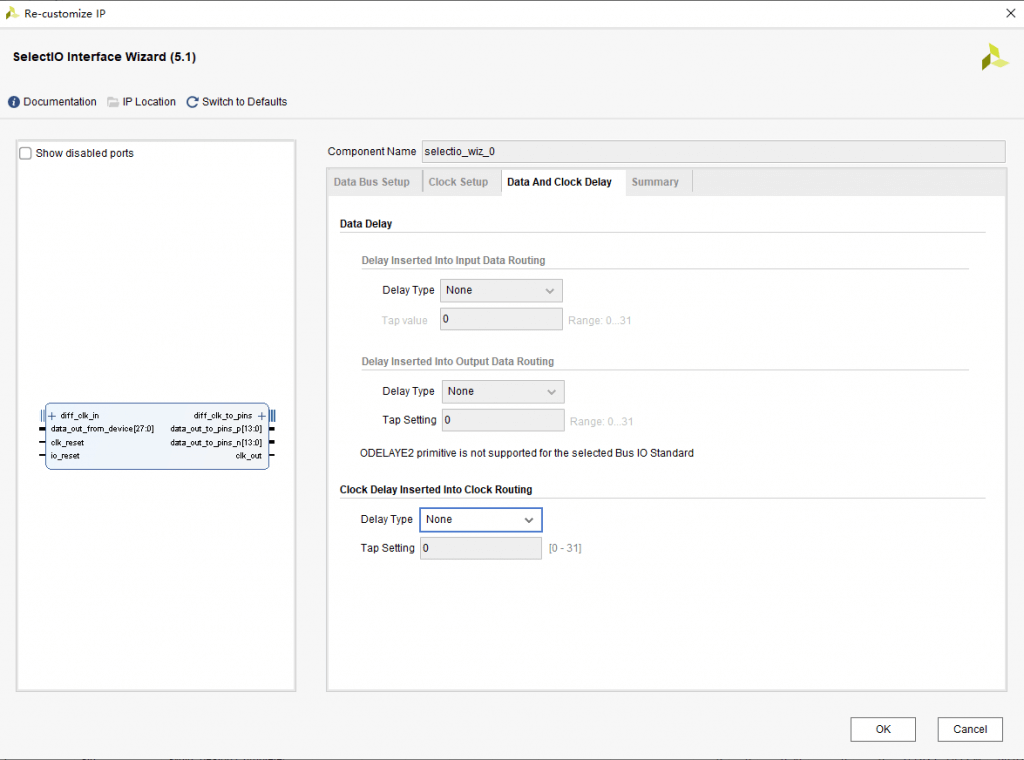

第三页则是一些时钟与数据的延迟,为了更好的做同步,这里没有配置。

当配置完整个selectIO,会发现他的数据输入有28位,而不是14位(DAC的位数),这是因为DDR是双边沿,所以他的数据是其位数的两倍。

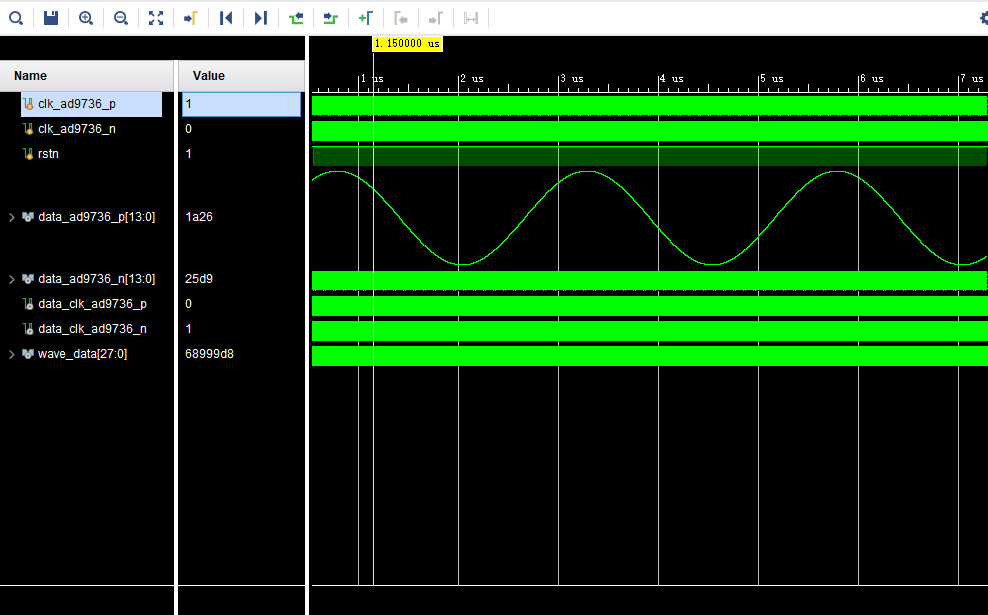

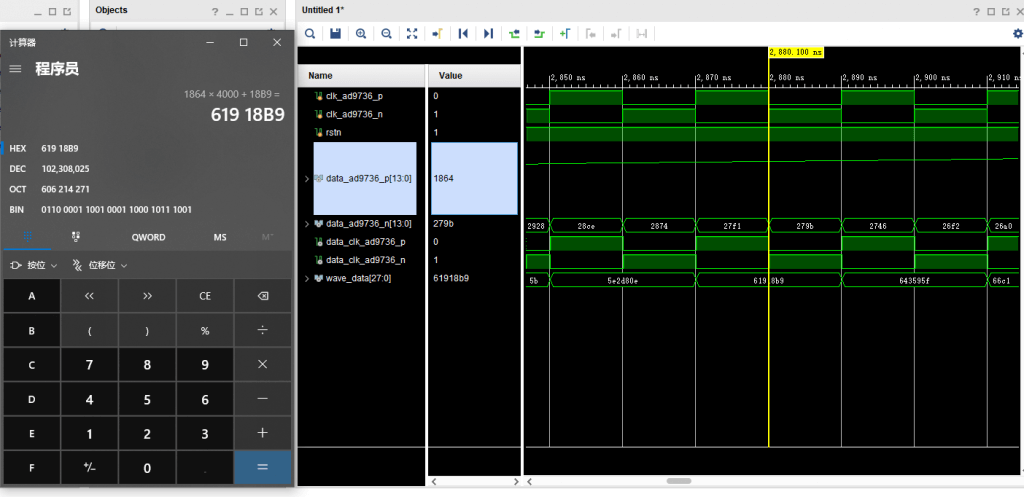

四、仿真

计算可得结果符合预期。

附、参考文献

1、【电路】LVDS 差分接口 - KevinChase - 博客园 (cnblogs.com)